# A Survey of Interconnection Networks Simulators

Journal Title

XX(X):1–26

©The Author(s) 2016

Reprints and permission:

sagepub.co.uk/journalsPermissions.nav

DOI: 10.1177/ToBeAssigned

www.sagepub.com/

SAGE

Atiyeh Gheibi-Fetrat<sup>1</sup>, Fatemeh Serajeh Hassan<sup>1</sup>, Negar Akbarzadeh <sup>2</sup>, Amir Mirzaei <sup>1</sup>, Mahmoud Reza Kheyrati-Fard <sup>1</sup>, Mohammad Hosseini <sup>1</sup>, Ahmad Javadi Nezhad <sup>1</sup>, Jeong-A Lee <sup>3</sup>, and Hamid Sarbazi-azad <sup>1, 2, \*</sup>

#### **Abstract**

Interconnection networks are essential for facilitating communication and resource sharing among multiple entities. These networks can be physical, connecting tangible hardware, or conceptual, linking abstract entities like social networks. The evaluation of interconnection networks is crucial for optimizing performance and ensuring performability, for which simulation is the most versatile and widely adopted approach. It provides flexibility for researchers to model various scenarios and configurations without the constraints of physical experimentation. This flexibility is particularly important as systems become increasingly complex and dynamic.

By utilizing simulation, researchers can identify potential bottlenecks and inefficiencies, leading to informed design decisions and enhancements. Various simulators have been developed for interconnection networks, each with specific strengths and limitations, but choosing the right simulator for a given scenario is challenging. In this paper, we survey notable interconnection network simulators and outline their advantages and disadvantages. We also provide detailed information about the most popular and famous interconnection network simulators. It helps researchers and developers to quickly review available interconnection network simulators and choose a suitable simulator for their specific purpose.

#### **Keywords**

Interconnection Networks; Performance Evaluation; Simulation; Network Simulators.

# Introduction

Any system involving multiple entities to accomplish common tasks, such as a computer system with various components, requires an inter-entity communication medium known as an interconnection network. This network facilitates communication, data sharing, and resource management across diverse devices and locations, which may include computers, smartphones, sensors, storage units, and other hardware.

Interconnection networks can also be conceptual, connecting two abstract entities, such as social networks that define relationships among individuals in different contexts, like social media and applications. Whether physical or conceptual, a network is best modeled as a graph, where the connection between two nodes is represented as an arc, and each node is considered a vertex. This creates a significant overlap between the fields of interconnection networks and graph theory.

Research in network-related fields often necessitates evaluation tools. Among the three primary evaluation methods—measurement, simulation, and analytical modeling—simulation is the most widely utilized by researchers and developers. Various simulators have been developed, each with specific strengths and limitations. Choosing the most appropriate simulator for a particular study can be challenging and requires a thorough understanding of the available options.

In this paper, we survey a wide range of notable network simulators, categorizing them and outlining their advantages and disadvantages, while providing detailed information about the most popular ones. This document serves as a resource for researchers and developers to efficiently review available network simulators and select the ones that best meet their needs.

In what follows, in Section 2, we first review the basics of interconnection networks and talk about different evaluation means and their advantages and disadvantages. In Section 3, we delve into simulation tools and categorize them. Notable network simulators at micro and macro levels and their characteristics are reported in Section 4 and Section 5, respectively. Finally, we conclude this study in Section 5.

# Interconnection networks and their evaluation

# Interconnection Networks

An interconnection network is a crucial component of any networked system because the overall efficiency of the

Email: atiye.gheibi@gmail.com, fatemeh.serajeh@ce.sharif.edu, akbarzadeh@ce.sharif.edu, amir.mirzaei79@sharif.edu, mahmoud.kheyrati222@sharif.edu, smh.hosseini992@sharif.edu, ahmadjavadi17@gmail.com, jalee@chosun.ac.kr, azad@sharif.edu

<sup>&</sup>lt;sup>1</sup> Sharif University of Technology , Tehran, Iran

<sup>&</sup>lt;sup>2</sup> Institute for Research in Fundamental Sciences (IPM), Tehran, Iran

<sup>&</sup>lt;sup>3</sup> Chosun University, Gwangju, South Korea

<sup>\*</sup> He is now a Visiting Research Professor at Chosun University under the Brain Pool (BP) Program of the National Research Foundation (NRF) of Korea.

system is very sensitive to network latency, throughput, and power consumption <sup>171</sup>. In addition to the technology, several key factors influence network efficiency: topology, switching method, and routing algorithm.

Topology Network topology defines the way nodes are connected and can be described using a graph 9 35 38. The vertices of this graph are the nodes, and the edges are the physical channels that connect the nodes. The network diameter is the maximum value (in hops) of the minimum distances between any two nodes in the network. The number of links adjacent to a node is called node degree, and network degree is the maximum node degree in the network 34. A network is regular if all nodes have the same degree. Finally, a network is symmetric if it is isomorphic to itself with any node labelled as origin 11 30. The best topology is one that is regular and symmetric with a small diameter and node degree 8.

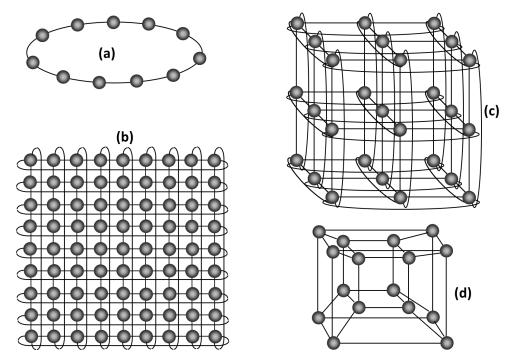

Many topologies have been proposed for interconnection networks, including the star, cube-connected cycles, generalised hypercube, pyramid, and k-ary n-cube. Figure 1 illustrates some of the most commonly used direct networks, the ring, 3-dimensional torus, and hypercube. These all belong to a major family of networks, called k-ary n-cubes, which have many desirable topological properties, including ease of implementation, modularity, symmetry, low diameter, and node degree, plus an ability to exploit locality exhibited by many parallel applications <sup>172</sup>.

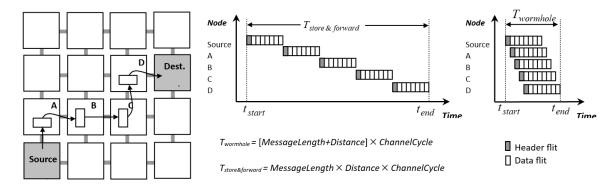

Switching Method Switching method determines the way messages visit intermediate nodes 40. Several methods have been described in the literature, of which the two most important are Circuit Switching and Packet Switching. Popular switching methods used in current networked systems are of packet switching type 740. Famous packet switching methods are store-and-forward<sup>29</sup> and virtual cutthrough (or VCT for short) 10 25 28 and its buffer limited variation wormhole switching <sup>26 39</sup>. In store-and-forward switching a node will not forward an incoming message till it has the entire message stored in its channel buffer. While most first-generation parallel computers employed storeand-forward switching VCT and wormhole switching have been widely used later due to its low buffering requirement and good performance 176. Here, a message is divided into flits (flow control unit) for transmission and flow control and each channel buffer needs to be only one flit in length. The first flit of a message, the header flit, includes the routing information and is followed by the data flits in pipelined fashion. If the header cannot be routed in the network due to contention for resources (buffers and channels), the data flits are also blocked in situ, keeping all the allocated buffers occupied <sup>176</sup>. Since wormhole routing uses pipelining, it can perform well even in a high diameter network<sup>34</sup>. Figure 2 illustrates the transmission of an 8-flit message from a source node to a destination node destined 5 hops away in a 4x4 mesh using store-and-forward and wormhole switching methods.

Because wormhole flits can be blocked in the network and then occupy switching resources, the method requires careful deadlock control. One solution to this problem is the use of virtual channel flow control <sup>150</sup> <sup>174</sup>. Flow control concerns techniques for dealing with contention by multiple messages

for the same channels and buffers. A good flow control policy should reduce congestion, be fair, and retain low latency. Flow control techniques are very dependent on the switching scheme employed; in wormhole routing, the commonest flow control strategy is the use of virtual channels <sup>174</sup>.

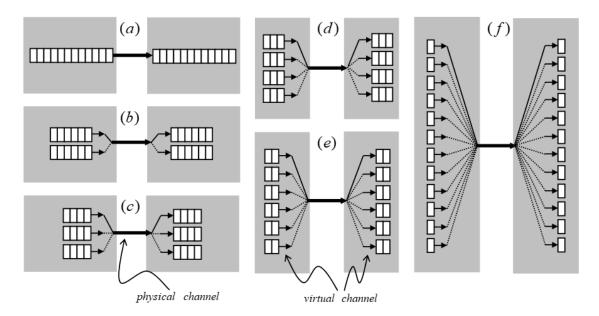

The preceding switching techniques assume that messages or parts of messages are buffered at the input and output of each buffer channel. Buffers are commonly operated as first-in-first-out (FIFO) queues. Therefore, once a message occupies a buffer for a channel, no other message can access the physical channel even if the message is blocked <sup>176</sup>. Due to the chained blocking property of wormhole switching, the bandwidth of interconnection networks is then limited to a fraction (20%-50%) of the total available physical bandwidth<sup>31 34</sup>. However, it is also possible to multiplex several communications on a flit-by-flit basis by decoupling the allocation of buffers and physical channels, thus dividing a physical channel into several logical or virtual subchannels 6. A virtual channel consists of a buffer—together with associated state information—capable of holding one or more flits of a message. Virtual channels were first introduced to prevent deadlocks in wormhole networks based on the torus routing chip. However, it has been shown that virtual channels can also be used to improve network performance and latency by relieving contention <sup>36</sup>.

Virtual channels dedicated to a physical channel may be organized in different ways. Figure 3 shows several organizations of virtual channels for a physical channel with a 12-flit buffer. The architectures differ in terms of performance, hardware requirements, and particularly arbiter complexity. Performance is dependent on network parameters, and there is an optimal number of virtual channels where the network performance is maximised <sup>32 33</sup>.

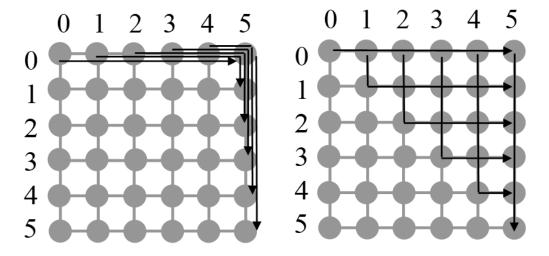

Routing Algorithm Most interconnection networks provide multiple physical paths for routing a message between two given nodes. This introduces the problem of choosing the best route among many possible alternatives. Routing is a means used to achieve this. An important requirement for any routing algorithm is to ensure deadlock freedom; deadlock situations occur when no message can advance towards its destination because of occupied channels and buffers<sup>27</sup>. Many practical networked systems have used deterministic routing with virtual channels to ensure deadlock avoidance if needed 33 88. This is achieved by forcing messages to visit the channels or virtual channels in a strict order<sup>34</sup>. Consequently, messages always take the same path between a given pair of nodes. This form of routing has the advantage of being simple but is unable to adapt to conditions such as congestion or failures. Dimension-ordered routing (DOR) is a typical example of deterministic routing where messages visit network dimensions in a pre-defined order. However, if any channel along the message path is heavily loaded, the message experiences large delays and if any channel along the path is faulty the message cannot be delivered at all. Adaptive routing improves both the performance and fault tolerance of an interconnection network and, more importantly, it has the ability to provide performance which is less sensitive to the communication pattern<sup>67</sup>. Figure 4 shows the channels that have available paths that can be taken by a message from node (0,0) to node (5,5) in a 6x6

Figure 1. Some popular topologies. (a) A ring (with 11 nodes), (b) 2-D torus (9x9 nodes), (c) 3-D torus (3x3x3 nodes), and (d) 4-D hypercube or 4-cube.

**Figure 2.** Transmission of an 8-flit message from the source node to the destination node destined 5 hops away in a 4x4 mesh (left) using store-and-forward (middle) and wormhole switching methods (right) via intermediate nodes A, B, C and D.

mesh with a deterministic XY routing algorithm and a fully adaptive routing algorithm.

#### Performance Evaluation and Simulators

Performance evaluation in various fields can be conducted through three primary means: measurement, simulation, and analytical modeling, each with its own advantages and disadvantages. Proper use of these three methods can lead to a more robust performance evaluation strategy. For instance, measurement can provide the foundational data needed for both simulation and analytical modeling. Simulations can test various scenarios informed by real-world measurements, while analytical models can offer theoretical insights that enhance understanding and interpretation of the measured and simulated data.

Measurement This involves collecting data from real systems or processes to assess performance metrics directly. Measurement is often the first step in performance evaluation, especially in environments where direct observation is feasible. This could involve using sensors, logging tools, or manual data collection techniques to gather performance

metrics such as response times, throughput, error rates, and resource utilization. The advantages of measurement-based evaluation include:

- Accuracy: Provides real-world data and insights.

- Relevance: Reflects actual performance under current conditions.

- *Immediate Feedback*: Allows for quick identification of issues.

However, disadvantages are:

- *Costly and Time-Consuming*: Setting up measurement systems can be expensive and require significant time.

- Limited Scope: May not capture all variables or scenarios.

- *Interference*: The act of measuring can sometimes alter system performance.

Simulation This method uses models to replicate the behavior of systems over time, allowing for the testing of different scenarios without impacting real operations. Simulation allows for the exploration of complex systems where direct measurement might be impractical or impossible. By creating a virtual model of a system, various scenarios can be

**Figure 3.** Organizing a 12-flit buffer dedicated to a physical channel; (a) conventional routers organize it into one FIFO queue, while a network using virtual channels may organize it into several independent lanes, resulting in different numbers of virtual channels each with different queue length, namely (b) two 6-flit, (c) three 4-flit, (d) four 3-flit, (e) six 2-flit, and (f) 12 1-flit buffers.

**Figure 4.** Routing messages in an 6x6 mesh from node (0,i) to node (i,5) (for  $i=0,1,\ldots,5$ ); (left) using dimension order routing, five messages must traverse the channel from (0,4) to (0,5); (right) using adaptive routing, all messages proceed simultaneously.

tested, including extreme conditions that may not be encountered in regular operations. Advantages of the simulation method are:

- Flexibility: Can easily modify parameters and test various scenarios.

- *Risk-Free Testing*: No impact on actual systems, allowing for exploration of "what-if" situations.

- *Visualization*: Often provides visual representations of performance metrics.

# Disadvantages include:

- *Complexity*: Developing accurate simulations can be complicated and require expertise.

- Data Dependency: The quality of results is highly dependent on the input data and assumptions.

- Computational Resources: May require significant computational power and time.

Analytical Modelling This involves using mathematical formulas and theories to represent system behavior and performance. It employs mathematical techniques to derive performance metrics based on theoretical constructs. This method is particularly effective in systems where relationships between variables can be clearly defined. Analytical models are desirable due to their important advantages, including:

- *Efficiency*: Can provide quick results with relatively low computational resources.

- Insightful: Can offer deep insights into system performance and underlying mechanisms.

- Scalability: Easily scalable to larger systems or different configurations.

However, advantages come with some disadvantages, namely:

- Simplifications: Often relies on assumptions that may not hold true in real-world scenarios, leading to inaccuracies.

- *Limited Applicability*: May not be suitable for highly complex or dynamic systems.

- Expertise Requirement: Developing accurate models requires a strong understanding of both the system and mathematical techniques.

Use of the Evaluation Methods Note that 1) measurement and simulation results can be used to validate analytical models; 2) simulations can be enhanced using measured data to ensure that the virtual models accurately reflect real-world conditions; 3) analytical models can be used to validate simulation results, ensuring that they align with theoretical expectations, and 4) analytical models can guide the development of simulations by identifying key variables and relationships that need to be included. Conversely, results from simulations can be used to refine analytical models, ensuring they are more representative of real-world conditions.

Considering all advantages and disadvantages of the three evaluation means, simulation has been the one most widely employed. Many simulators of networked systems have been developed, introduced, and used by the researchers. In what follows, we will try to introduce, categorize, and explain some important ones in more details. Such a survey can be very useful for researchers, engineers, and students to properly select the simulator that best suits their purpose.

# **Simulators**

The growing complexity of contemporary systems, which includes integrated circuits and global communication networks, necessitates the utilization of a potent tool called the simulator. They enable engineers and researchers to perform thorough analyses and improvements on network systems before they are physically created or deployed in the real world.

To best understand the various options available, we can categorize simulators into three main groups based on their scale and specialization: 1) Micro-scale network simulators which focus on intricate details of individual network components like routers and switches, and excel at modeling low-level protocols and hardware interactions within a small network, 2) Macro-scale network simulators which deal with larger network scenarios, typically focusing on internetworking and routing protocols across geographically dispersed areas, and finally, 3) specialized network simulators that caters to specific network types, such as wireless sensor networks or mobile ad-hoc networks. Each category offers unique advantages depending on the specific network behavior you want to analyze.

In the following subsections, we will delve into each category to better understand their unique capabilities and applications.

# Micro-Scale Network Simulator

These simulators focus on interconnection networks in small-sized on-chip or on-board systems and for a limited number of interconnected devices. They are particularly useful for examining detailed interactions within networks with small geometry, including the performance and behavior of individual components.

One of the most important and popular micro-scale networks is on-chip networks or network-on-chips. Simulators for network-on-chip are essential in analyzing and enhancing the efficiency of on-chip interconnections in multi-processor systems. Various simulators have been developed to facilitate the design and testing of NoCs <sup>45</sup>. These simulators allow for the evaluation of various topologies, e.g., mesh and torus, taking into account factors such as latency, power consumption, and resource utilization. Efforts have been undertaken to migrate CPU-based simulators, like NEST, to diverse hardware platforms such as GPUs and FPGAs. This is aimed at enhancing the performance and expandability for conducting large-scale simulations <sup>3</sup>. These advancements allow researchers to efficiently investigate and enhance on-chip network configurations.

#### Macro-Scale Network Simulator

These simulators handle larger-scale networks, focusing on the interactions and performance of extensive network infrastructures. They are essential for studying the behavior of complex networks that span large geographical areas, including local, metropolitan, and wide-area networks. The following subsections explore different types of macro-scale network simulators.

Local Area Network Simulators Local Area Network (LAN) simulators model and mimic the operation of network designs to determine performance metrics like throughput, delay, and packet loss 92 93 94 95. These simulators aid in optimizing network performance before actual implementation, crucial for both wired and wireless LANs. Examples include OPNET Modeller for wireless LANs and special-purpose languages like GPSS and SIMSCRIPT for general LAN simulations. Simulation parameters commonly analyzed in such simulators encompass throughput, delay, packet loss, processing time, and network capacity, among others. By utilizing these simulators and evaluation parameters, network engineers can assess and enhance LAN performance, identify bottlenecks, and plan for future network capacity requirements effectively.

Metropolitan Area Network Simulators Metropolitan Area Networks (MANs) are a type of network designed to cover larger geographical areas than LANs, but within the boundaries of a city or metropolitan region. One of their primary functions is to interconnect various local access networks, even when those networks use different technologies. MANs offer significant advantages, including high bandwidth, low latency, and reliable transmission quality. As a backbone network, a MAN can connect many LANs, facilitating efficient communication across the city. However, MANs are optimized for metropolitan-scale deployments and would need substantial modifications to be effective for Wide Area Networks (WANs) that span across greater distances <sup>173</sup>.

To model and evaluate MAN performance, simulators employ various techniques to replicate the behavior of network traffic and infrastructure. One common approach is to use discrete event simulators for optical Wavelength

Division Multiplexing (WDM) networks, which enable detailed analysis of metrics such as network delay, packet loss, and bandwidth utilization, particularly in WDM unidirectional slotted ring networks <sup>96 97</sup>. These simulators take into account several key factors, including network topology, traffic patterns, latency-sensitive protocols, and redundancy strategies, to ensure high performance and reliability in MAN environments <sup>98 99</sup>.

*Wide Area Network Simulators* Wide Area Network (WAN) simulators emulate the behavior of large-scale networks to evaluate performance and test various scenarios. Examples include NS2, NS3, OMNET++, QUALNET, and GUTS <sup>100 101</sup>. These simulators offer various simulation parameters such as network mobility support, realistic internet-scale topologies, artificial latency, bandwidth limitation, and throughput statistics display <sup>102 201</sup>. By utilizing these simulators, researchers and practitioners can analyze network behavior, assess the impact of different configurations, and optimize network performance without the need for costly real-world implementations, thus facilitating costeffective and efficient network research and development <sup>104</sup>.

# Specialized Network Simulators

These simulators focus on specific network types or technologies, allowing for a more targeted analysis and optimization. They are particularly useful for studying unique network behaviors and performance metrics in specialized environments. The following subsections examine different types of specialized network simulators.

Software-Defined Networking (SDN) Simulator By decoupling the control plane from the data plane, Software-defined networking (SDN) allows for centralized control, automation of network tasks, and improved network design, management, and optimization<sup>59</sup>. SDN simulators are crucial tools used to validate proposed solutions before deployment in real networks, especially in complex and costly environments <sup>56</sup>. These simulators help in replicating network scenarios, measuring traffic flow, improving packet loss rates, and enhancing bandwidth utilization<sup>57</sup>. SDN simulators, such as Mininet and Miniedit, enable the simulation of SDN networks to evaluate performance under various operational conditions and security threats 58. SDN simulators play a vital role in testing and validating SDN solutions, contributing to the advancement and adoption of this innovative networking technology 60.

Mobile Network Simulators A Mobile Ad-hoc Network (MANET) is a key focus in wireless communication research. It comprises some nodes that communicate via wireless links, without relying on a fixed infrastructure and backbone, or centralized control. To evaluate the behavior and performance of communication protocols in MANETs, researchers employ various methods. MANET simulators, in particular, play a crucial role in helping network developers verify the functionality and efficiency of MANETs in real-time scenarios <sup>175</sup>. Several platforms are available for simulating and testing MANET routing protocols, each with its own strengths. While no single simulator comprehensively covers all aspects of MANETs, some tools stand out. NS-3 is widely regarded for its

broad protocol support across multiple layers, making it a top choice for MANET simulations. GloMoSim is highly scalable and particularly well-suited for simulating networks with large numbers of nodes. OMNET++ is another valuable option, known for its powerful graphical user interface (GUI), which enhances user experience and simulation visualization <sup>175</sup>.

Network Security Simulators A network security simulator functions by integrating attack simulation, risk simulation, and security defense simulation subsystems to model various attack scenarios, adjust security defense strategies, and evaluate network security measures. Examples of network security simulators include Nessi2, which focuses on distributed and security simulations 85, and the Graphical Network Simulator (GNS3), which utilizes Kali Linux for penetration testing and security audits, allowing for the emulation of diverse network components and configurations to assess network vulnerabilities and performance 86. Various simulators like NS2, NS3, OMNeT++, NetSim, REAL, OPNET, and QualNet offer different features, advantages, and disadvantages, catering to specific simulation requirements in wired and wireless networks 87. These simulators enable users to simulate network topologies, analyze performance, and test security measures efficiently and cost-effectively.

Internet of Things Simulators Internet of Things (IoT) network simulators play a crucial role in analyzing and predicting the performance of IoT deployments 82. These simulators must accurately replicate the behavior of network components at all levels of the system stack <sup>83</sup>. Various simulators have been developed for IoT and wireless sensor networks (WSNs), such as NS3, OMNeT++ (FLoRa), and LoRaSim, focusing on technologies like LoRa (Long Range) communication <sup>84</sup>. These simulators are evaluated based on parameters like Packet Delivery Ratio (PDR), utilization, memory usage, execution time, and collision rates to assess their performance in simulating IoT networks effectively. By utilizing these simulators and corresponding parameters, researchers can simulate IoT systems and applications before actual deployment, ensuring better performance and reliability.

# Notable Network Simulators at Micro-Scale

In the previous sections, we categorized network simulators into three main groups: Micro-Scale Network Simulators, Macro-Scale Network Simulators, and Specialized Network Simulators. Each category serves unique purposes and offers distinct advantages based on the scale and specific network behaviors they aim to analyze.

This section introduces some of the most renowned simulators dedicated to micro-scale environments, providing a comprehensive view of their key features, strengths, and weaknesses. Furthermore, we will conduct a comparative analysis of these simulators to underline where each stands out. This assessment aims to equip researchers and industry professionals with the insights needed to choose the most effective simulation tools for their granular network research and development activities.

# Supersim

SuperSim<sup>2</sup> is an open-source, flit-level interconnection network simulator designed specifically for evaluating the complexities of large-scale high-performance networks. It excels at providing a detailed model of network architectural intricacies, which is crucial for examining the performance implications of various router microarchitectures and adaptive routing algorithms. SuperSim offers a flexible and extensible simulation framework, allowing for quick modeling of systems through a programmer-centric approach. Its hierarchical abstract interface facilitates easy integration of component models, and it is complemented by a comprehensive suite of tools for efficient simulation management, analysis, and visualization through Python scripting.

SuperSim excels in offering in-depth modeling of interconnection network architectures, making it particularly effective for performance analysis of router microarchitectures and adaptive routing. It enables quick and straightforward system modeling through a flexible simulation framework designed to enhance programmer productivity. This is achieved by allowing the easy integration of new component models and facilitating the addition of new components and configurations via its hierarchical abstract interface. Furthermore, SuperSim includes tools for efficient management, analysis, and visualization of simulations using Python scripting. It supports multiple levels of simulation accuracy, from cycle-accurate to higher-level abstractions, adjustable according to the study's needs.

However, the detailed and flexible nature of SuperSim may pose challenges for users who are not well-versed in simulation frameworks. Additionally, its primary focus on large-scale network simulations might limit its applicability to smaller system designs. Certain idealized assumptions, such as those concerning congestion credit accounting and flow control techniques, may also lead to inaccurate performance predictions.

#### **Booksim**

BookSim<sup>220</sup> is a cycle-accurate simulator designed for Network-on-Chip (NoC) architectures and other interconnection networks<sup>12</sup> 13. It emphasizes simulation flexibility and accurate modeling of network components, including configurable parameters like topology, routing algorithm, flow control, and router microarchitecture. BookSim2 <sup>14</sup> enhances these capabilities by introducing detailed modeling of router microarchitecture, supporting additional traffic models, and accurately simulating inter-router channel delays. The enhancements in BookSim2 focus on providing a more realistic and detailed simulation environment, validated through comparisons with RTL implementations, offering insights into various networking aspects.

BookSim provides a high degree of flexibility and modeling fidelity, making it ideal for evaluating novel network designs with cycle-accurate precision. Validated against RTL implementations of NoC routers, BookSim ensures the accuracy of simulation results. By using this detailed network simulator, researchers can understand the impact of accurately modeling the router pipeline on network performance. The updated version, BookSim2, enhances the simulation capabilities further by including detailed router

microarchitecture modeling and supporting additional traffic models.

However, compared to some event-driven simulators, BookSim may run slower, especially under low to medium network load scenarios. Moreover, configuring and utilizing advanced features like dynamic buffer management and traffic class differentiation requires substantial effort and familiarity with the system, which may pose challenges for some users.

#### Noxim

The Noxim simulator 15 is a cycle-accurate Network-on-Chip (NoC) simulator that allows for the analysis of performance and power statistics of both wired and wireless NoC designs 16. It is Developed using SystemC, a system description library written in C++. It offers the flexibility to modify network size, packet size, routing algorithms, and packet injection rates, enabling the evaluation of various parameters such as throughput, delay, energy consumption, and network traffic distributions <sup>17</sup>. Noxim is widely used due to its open-source nature, support for wireless networks, and the ability to simulate mesh wireless NoC architectures <sup>23</sup>. However, the original Noxim simulator lacks accuracy in power and thermal estimations due to the absence of temperature/power cross-impact considerations, which is addressed by the PAT-Noxim simulator<sup>24</sup>, providing more precise power and temperature estimations for a wide range of VLSI technologies. Additionally, the original Noxim does not support trace-driven workloads. Pires et al. <sup>17</sup> enhance Noxim to run real trace-driven networks, thereby expanding its applicability.

Noxim is a versatile simulator capable of modeling both heterogeneous wired and wireless NoC architectures, making it an effective framework for exploring the design space of NoC-based systems. Its modular design allows researchers to easily add or modify components such as routing algorithms and traffic models, which significantly enhances research flexibility. Additionally, PAT-Noxim provides detailed statistics for evaluating performance and power metrics and supports the inclusion of new features and algorithms using standard C++ code. This flexibility is further augmented by its support for both cycle-accurate simulation and Transaction-Level Modeling, catering to varying simulation needs.

However, users unfamiliar with SystemC and C++ may need some acclimatization to effectively utilize Noxim's features. Additionally, while cycle-accurate simulation offers precision, it can be computationally intensive and time-consuming. These aspects may pose challenges, particularly in scenarios requiring rapid prototyping or large-scale simulations. Nevertheless, Noxim's comprehensive capabilities make it a powerful tool for in-depth NoC research and development.

#### Orion V3

ORION3<sup>43</sup> is a comprehensive tool designed for Networkon-Chip (NoC) router estimation, focusing on accurate power and area estimation methodologies within manycore architectures. The simulator employs both parametric and non-parametric modeling techniques, enabling users to

derive models directly from actual physical implementation data, achieving average estimation errors of no more than 9.3% across various parameters. Developed as an opensource tool, ORION3.0 supports extensive microarchitecture configurations and multiple router RTL (Register Transfer Level) generators. It enhances flexibility by allowing customization of key parameters such as the number of ports and virtual channels. Additionally, ORION3.0 integrates advanced non-parametric regression techniques like radial basis functions and support vector machine regression, which provide robust estimations. While achieving high accuracy for power and area modeling, ORION3.0 also maintains backward compatibility with its predecessor, ORION2.0 18, by including logic template-based models.

ORION3 discussed offers significant strengths in improving accuracy for power and area predictions in microarchitectural designs. Its extensible and configurable architecture allows customization of key parameters, such as the number of ports and virtual channels, facilitating a wide range of applications. By leveraging advanced non-parametric regression techniques like radial basis functions and support vector machine regression, the model provides robust estimations grounded in actual physical implementation data. This enhances the reliability of the predictions and enables more precise design optimizations.

However, achieving maximum estimation accuracy requires users to supply high-quality training and testing datasets, which can be challenging without access to precise and comprehensive data. Additionally, the integration of advanced modeling techniques can be complex and may require a sophisticated understanding of statistical modeling and regression. This can be a barrier for users who lack expertise in these areas, potentially limiting the tool's accessibility and ease of use. Nevertheless, the strengths of ORION3 make it a powerful resource for those seeking detailed and accurate predictions in microarchitectural design.

## SunFloor-3D

SunFloor-3D<sup>45</sup> is a design tool for synthesizing applicationspecific 3D NoCs, addressing the challenges of integrating efficient interconnects in 3D SoCs 44. It determines optimal topologies, paths for communication flows, and component placement across 3D layers, showcasing significant improvements in power consumption (average of 38%) and delay (average of 13%) compared to 2D implementations 46.45. The tool offers advantages such as enhanced performance, reduced power consumption, and minimized delays, making it a valuable asset for designing efficient 3D NoCs. However, challenges may include complexity in design optimization, potential resource constraints, and the need for specialized expertise in utilizing the tool effectively. Overall, SunFloor 3D proves to be a beneficial solution for optimizing 3D NoC designs, balancing performance gains with potential design complexities and resource requirements.

SunFloor-3D distinguishes itself by integrating various design methods specifically tailored for synthesizing custom NoCs that address the unique challenges posed by 3D integration technologies. This simulator allows for extensive customization, enabling users to tailor designs to specific application needs, which can lead to optimized performance

metrics. The ability to adapt and fine-tune network parameters ensures that the resulting NoC architectures are highly efficient and performance-driven.

However, designing for 3D ICs introduces additional complexity, particularly in managing the maximum number of Through-Silicon Vias (TSVs) and handling vertical interconnections. These factors can create significant challenges in achieving effective implementation, as careful consideration and management of vertical links are critical to maintaining feasible and high-performing 3D NoC designs.

# **HNOCS**

HNOCS (Heterogeneous Network-on-Chip Simulator) is a modular, open-source NoC simulator based on OMNeT++ 126. It supports modeling heterogeneous NoCs with variable link capacities and varying numbers of virtual channels per port, addressing diverse traffic needs. The simulator includes three types of routers—synchronous, synchronous virtual output queue (VoQ), and asynchronous and offers detailed statistical measurements at both the flit and packet levels. Built on OMNeT++, HNOCS benefits from easy traceability, debugging utilities, and support for arbitrary topologies, making it highly extendible and scalable. It allows flexible traffic configuration and comprehensive performance evaluation, making it a versatile tool for advanced NoC research and design exploration.

One of primary strengths of HNOCS is its efficient simulation management. Leveraging the robust features of OMNeT++ for parallelism and flexible topology definition, HNOCS significantly reduces simulation run-time and complexity. This makes it an excellent tool for researchers looking to investigate the diverse aspects of heterogeneous NoC designs. However, any limitations or bugs within the OMNeT++ framework can directly impact HNOCS. Users might need to rely on the OMNeT++ community for fixes and updates, which can be a constraint in terms of timely resolution and support.

# Nirgam

NIRGAM <sup>155</sup> is a cycle-accurate, discrete event simulator based on SystemC, designed for research in the field of Network on Chip (NoC). It provides a platform to experiment with NoC design, including routing algorithms and applications on various topologies. The simulator supports mesh and torus topologies, and can simulate different routing algorithms, buffer depths and configurable traffic patterns.

Nirgam simulator is highly regarded for its ability to provide detailed performance metrics, including latency and throughput, which are essential for effectively evaluating NoC designs. The simulator offers users the flexibility to configure various NoC parameters such as topology size, clock frequency, buffer depth, flit size, and the number of virtual channels. This allows for in-depth customization and fine-tuning to meet specific project needs, thereby enhancing the overall evaluation and optimization process.

However, Nirgam suffers from insufficient documentation, which can make it difficult for users to fully understand and leverage its features. This lack of comprehensive guides and support materials may hinder new users or those unfamiliar

with the simulator. Additionally, Nirgam does not support a wide range of network topologies, which may limit its applicability for diverse research projects that require exploring various NoC configurations.

#### **ATLAS**

ATLAS 91 is an automated environment designed for the generation and evaluation of Networks-on-Chip (NoCs). It supports various NoC architectures, including those proposed by the GAPH Group 221. The environment is implemented in Java, allowing execution across different hardware and software platforms. Key functionalities include tools for NoC generation, traffic generation, simulation, traffic evaluation, and power evaluation. Specifically, the NoC Generation tool allows users to configure network dimensions, bandwidth, and various routing algorithms, while the Traffic Generation tool enables the creation of different traffic patterns for simulation purposes. The evaluation tools help analyze performance metrics such as latency, throughput, and power consumption, providing comprehensive feedback for optimization.

S simulator stands out due to its ability to automate NoC generation and evaluation, significantly reducing design time and effort for researchers and engineers. It encompasses a comprehensive suite of tools for NoC generation, traffic generation, simulation, and power evaluation, making it an all-in-one solution for NoC prototyping and analysis. One of its key strengths is the capability to prototype NoCs on Xilinx FPGAs, allowing for practical testing in real-world scenarios. Additionally, ATLAS provides detailed reports on performance and power consumption, aiding in thorough evaluation and optimization. Its versatility makes it suitable for both academic research and industrial applications, especially in the telecommunications sector. However, it requires external VHDL/SystemC simulators, which can involve additional costs and setup efforts. Moreover, the simulator's extensive features and numerous configurable parameters can pose challenges for new users, necessitating a steep initial effort to become proficient with the tool.

# MC-Sim

MC-Sim <sup>137</sup> is an efficient simulation framework designed to model heterogeneous multi-core systems. It integrates diverse components like processor cores, memories, custom hardware blocks, and network-on-chip (NoC) architectures on a single chip. MC-Sim provides rapid and accurate performance estimation, supporting various processor, memory, and NoC configurations. A key feature is its ability to generate fast, cycle-true behavioral C-based simulators for coprocessors using high-level synthesis, achieving significant speed improvements over RTL descriptions. MC-Sim allows for the simulation of complex real-life applications, enabling designers to explore and optimize MPSoC designs efficiently.

The MC-Sim simulator excels in enhancing simulation speed, achieving an impressive average 45x speedup relative to RTL descriptions. This performance leap allows for more efficient modeling of complex systems. It provides cycle-true simulation, ensuring accurate performance modeling and is capable of modeling real-life applications with a minimal

deviation of just 7% from actual implementations. MC-Sim offers extensive configurability for processors, memory systems, and NoC architectures, supporting the integration of both loosely-coupled and tightly-coupled coprocessor models. The simulator can handle systems with up to 64 or more active superscalar cores and supports multitasking, making it adept at managing workloads composed of multiple single-threaded or multi-threaded applications.

However, leveraging MC-Sim to its fullest potential requires users to have a strong understanding of multicore processor architecture, memory systems, and NoC configurations. Additionally, the simulator lacks an energy model and does not calculate energy consumption, which limits its comprehensiveness in terms of evaluating energy efficiency.

#### **VNOC**

VNOC 2.0<sup>222</sup> is a versatile Network-on-Chip (NoC) simulator developed from its predecessor VNOC 1.0. It is primarily implemented in C++, featuring a straightforward and clean codebase with abundant comments for ease of understanding. Key features include a simple graphical user interface (GUI), an ability to simulate various traffic types (such as uniform random, transpose, hotspot, and self-similar traffic using Glen Kramer's generator<sup>223</sup>), and integrated Orion 2 and 3 power models for power consumption estimates. VNOC 2.0 supports Dynamic Voltage and Frequency Scaling (DVFS) strategies, allowing users to implement and study their own DVFS ideas easily.

The VNOC simulator is distinguished by several strengths that make it a powerful tool for NoC research and development. Its graphical user interface (GUI) significantly enhances usability, allowing users to visualize simulations more effectively, although this feature may slightly extend runtime. VNOC 2.0's capability to simulate a variety of traffic patterns adds to its versatility, making it highly suitable for diverse research scenarios. The integration of embedded power models, specifically Orion 2 and 3, allows for precise power consumption estimates, which is critical for studies focused on energy efficiency. Additionally, VNOC's support for dynamic voltage and frequency scaling (DVFS) offers users the flexibility to experiment with different voltage and frequency scaling techniques, further broadening its applicability.

On the downside, the VNOC simulator requires users to manually edit source files to adjust buffer sizes for accurate power estimations, adding complexity to the setup process. The integration process for Orion power models is not automated, demanding manual coding changes and recompilation, which can be laborious and time-consuming. Furthermore, while the simulator is available for free for noncommercial use, it necessitates permission for commercial applications, potentially limiting its accessibility based on the users' intentions.

# **AcENoCs**

The AcENoCs (Accelerated Emulation platform for Network-on-Chips) <sup>139</sup> is a configurable hardware/software platform designed for FPGA-accelerated emulation of Network-on-Chip (NoC) architectures. It aims to

validate synchronous and Globally Asynchronous Locally Synchronous (GALS) based NoC architectures <sup>224</sup> with high speed and accuracy. The platform consists of reconfigurable network components, traffic generators and ejectors, and modules for statistics collection and analysis. It supports the exploration of various router features and network configurations, allowing users to perform quick design validations and optimizations. AcENoCs achieves significant performance improvements over traditional HDL and software simulators, with speedups ranging from 10000-12000X and 14-47X, respectively.

AcENoCs simulator boasts several key strengths, such as its ability to maintain cycle-accurate emulation, which is critical for validating timing-sensitive designs reliably. The platform supports the easy reconfiguration of emulation parameters and integrates a variety of router architectures and network-on-chip topologies. Additionally, it leverages a co-design approach that efficiently uses FPGA resources: hardware manages the network components while software oversees traffic generation, statistics analysis, and configuration. However, the simulator does have some limitations. The size of the network-on-chip (NoC) that can be emulated is restricted by the available FPGA resources, posing a challenge for larger network designs. The initial setup and integration of hardware and software components can be complex, demanding significant expertise from users. Furthermore, reconfiguring hardware components can introduce overhead and require time-consuming modifications, which can hinder rapid prototyping.

#### DART

The DART simulator <sup>140</sup> is a flexible and efficient FPGA based architecture designed for simulating Networks-on-Chip (NoCs) to meet the growing demand for on-chip communication bandwidth in multi-core systems. It virtualizes NoC components, mapping them to a generic simulation engine on an FPGA, allowing any NoC design to be simulated without resynthesizing the FPGA. DART achieves over 100 times speedup compared to traditional cycle-based software simulators while maintaining accuracy. Its architecture includes configurable components like traffic generators, routers, and flit queues, synchronized by a global time counter, optimizing for area efficiency and enabling larger NoC simulations within FPGA constraints. This eliminates the need for time-consuming FPGA resynthesis, providing a powerful, high-speed, and accurate simulation tool.

The DART simulator offers several significant advantages for Network-on-Chip (NoC) design simulation. Notably, it allows any NoC design to be simulated without the need to resynthesize the FPGA, saving considerable time and effort compared to traditional FPGA-based emulators. DART achieves more than 100 times speedup over cycle-based software simulators, ensuring rapid simulation without compromising accuracy. Its architecture is optimized for area efficiency, enabling the simulation of larger NoC designs within the FPGA's capacity constraints. Moreover, DART features configurable components, such as traffic generators, routers, and flit queues, which can be adjusted at runtime to simulate various NoC designs and behaviors. Despite these strengths, there are some limitations. The size of the

NoC that can be simulated remains bound by the physical capacity of the FPGA. The setup and configuration process of the DART simulator, while flexible, can be complex and requires a deep understanding of NoC architectures and FPGA programming. Additionally, users must have access to suitable FPGA hardware, which may not be feasible for all users or institutions. Interacting with the simulator can introduce latency due to Input/Output overhead, particularly under high traffic conditions, affecting the overall simulation efficiency.

# NoCTweak

NoCTweak <sup>70</sup> is an adaptable and open-source simulator, specifically crafted for analyzing the performance and energy efficiency of Network-on-Chip (NoC) architectures. Utilizing SystemC, NoCTweak ensures cycle-level precision and supports various settings, including diverse router types (such as wormhole, virtual-channel, and bufferless), network dimensions, routing protocols, and traffic schemes. It provides extensive statistical outputs, offering insights on metrics like average network latency, throughput, and router power consumption. The simulator leverages post-layout power data obtained from commercial CMOS standard-cell libraries to ensure accurate energy evaluations. Designed for the initial phases of many-core chip designs, NoCTweak facilitates rapid and flexible modeling of concurrent hardware modules.

The NoCweak simulator stands out by offering extensive customization capabilities for network and router parameters, which allows for highly tailored simulations suited to specific design needs. It provides thorough statistical outputs that enable detailed analysis of network performance and energy efficiency. Additionally, the simulator leverages accurate power and timing data from standard-cell libraries, ensuring the reliability of its simulation results. On the downside, NoCweak primarily supports 2-D mesh networks, which might pose a limitation for users interested in simulating more complex or varied network topologies. This focus can restrict its applicability to a broader range of designs and simulations.

# **DARSIM**

DARSIM <sup>106</sup> is a highly configurable, parallel cycle-level network-on-chip (NoC) simulator designed to evaluate routing and virtual channel (VC) allocation algorithms. It supports extensive customization of hardware parameters and various traffic generation methods, including trace-based injectors and a built-in MIPS simulator. DARSIM utilizes a multithreaded simulation engine to distribute tasks across multiple cores, offering both cycle-accurate and performance-optimized simulations. Its open-source nature under the MIT license promotes accessibility. The simulator can operate in network-only mode or integrate with a MIPS-based multicore system, supporting MPI-style applications. DARSIM's design helps researchers explore NoC design space and assess performance impacts, aiding in the development of efficient multicore processors.

The DARSIM simulator offers several significant strengths, particularly its detailed customization of hardware parameters, routing, and virtual channel (VC) allocation

algorithms, making it highly adaptable for various research and design needs. Its ability to leverage multiple cores for simulation tasks enhances performance, enabling faster simulations. It supports both trace-based traffic injection and cycle-level MIPS simulation, accommodating multiple traffic patterns and application scenarios. Additionally, DARSIM injects randomness to break arbitration ties, thereby reducing biases in traffic patterns and improving the fairness of simulations.

That said, DARSIM also has its drawbacks. Its multithreaded simulation, while providing speed, can be quite resource-intensive, necessitating powerful multicore processors to fully benefit from its capabilities. This high demand for processing power could be limiting for users without access to such robust hardware.

# AdapNoC

AdapNoC <sup>142</sup> is a configurable, cycle-accurate FPGA-based Network-on-Chip (NoC) simulator designed to evaluate various NoC architectures and configurations. It supports a wide range of configurable parameters via software, operates with a dual-clock architecture, and includes a traffic aggregator for adaptive routing algorithms. By offloading some components, such as Traffic Generators (TGs) and Traffic Receptors (TRs), to software, AdapNoC enhances simulation speed and optimizes FPGA resource usage. The architecture allows for the simulation of both virtualized and non-virtualized networks, making it particularly beneficial for exploring many-core system designs. AdapNoC achieves significant speed improvements, demonstrating a 53x to 180x speed-up compared to traditional software simulators like Booksim.

The AdapNoC simulator offers notable strengths, including extensive configurability of NoC parameters such as topology, routing protocols, flow control mechanisms, and buffer sizes. It supports both non-virtualized and virtualized configurations, enabling the simulation of networks with up to 1024 nodes. Additionally, AdapNoC incorporates a centralized traffic aggregator and supports table-based adaptive routing algorithms, which enhances its routing simulation capabilities. By balancing hardware and software aspects, AdapNoC effectively leverages the strengths of both, contributing to improved overall simulation performance.

Nevertheless, AdapNoC has some weaknesses. The hard-ware/software co-design and extensive configurability can make it more complex to set up and use compared to simpler simulators. Despite various optimizations, it still demands significant FPGA resources, which poses a limitation for very large-scale simulations or for users with constrained hardware capabilities. Lastly, the virtualization process can introduce additional complexity in synchronizing intra-cluster and inter-cluster transmissions, potentially affecting performance and increasing the difficulty of maintaining simulation accuracy.

#### Garnet

The GARNET simulator <sup>163</sup> is a detailed, cycle-accurate model of an on-chip interconnection network integrated into the GEM5 full-system simulation framework. It accurately models a five-stage pipelined router with virtual channel flow

control and includes detailed microarchitectural components like flit-level input buffers, routing logic, allocators, and the crossbar switch. This precision allows GARNET to capture realistic interactions between the memory hierarchy and the interconnection network, essential for accurate CMP design simulations. GARNET enables the evaluation of different network configurations and optimization techniques on full-system performance, such as comparing shared and private L2 cache configurations and assessing the benefits of Express Virtual Channels (EVCs). By providing detailed system-level insights, GARNET is a valuable tool for CMP system design and research.

The Garnet simulator excels in providing a cycleaccurate model of on-chip interconnection networks, capturing detailed aspects of router microarchitecture such as flit-level buffers, routing logic, and virtual channel (VC) flow control. By integrating with the GEM5 fullsystem simulator, Garnet allows for accurate simulations of CMP systems, reflecting realistic interactions between the memory hierarchy and interconnection network. It supports comprehensive evaluations of various network configurations and optimization techniques, aiding in decisions about shared vs. private L2 cache configurations and the impact of techniques like Express Virtual Channels (EVCs). Additionally, it includes performance counters for detailed performance analysis, which are crucial for optimizing system efficiency. Garnet can model networks with diverse topologies and configurations, making it suitable for studying future CMP systems with dozens to hundreds of nodes.

However, Garnet has its downsides. Its detailed modeling can lead to increased simulation overhead, slowing down simulations, especially for large-scale systems or realistic workloads. The complexity and depth of Garnet's features can be challenging for new users to learn and effectively utilize. Researchers focusing on low-level interconnection issues might find trace-driven simulation methods more appropriate, as Garnet's full-system approach may be unnecessarily complex for their needs. Since Garnet is integrated with GEM5, any limitations or issues within GEM5 can potentially affect Garnet's performance and accuracy. Additionally, the detailed simulations require significant computational resources, which can be a limitation for some research groups or applications.

### **Xmulator**

XMulator is a listener-based, integrated simulation platform designed to evaluate multicomputer interconnection networks. It provides a flexible, object-oriented, and multilayered environment, allowing easy extension and independent development of different network components. XMulator supports various network topologies, routing algorithms, and switching techniques, and it is the first simulator capable of simulating any arbitrary interconnection topology, including those with faults. The simulator uses XML for defining topologies, parameters, and outputs, enhancing flexibility and interoperability. It is implemented in C# and employs modern software architecture paradigms to facilitate the modeling and performance evaluation of multicomputer networks <sup>203</sup>.

Xmulator boasts several strengths, including its flexibility and extensibility, thanks to its object-oriented design and listener-based integration, which allow for easy extension and modification of the simulation environment without altering existing models. It offers a comprehensive toolbox with a wide range of network topologies, routing algorithms, switching techniques, and router models, making it versatile for various network designs. The XML-based configuration provides high flexibility and user-friendliness, simplifying the definition of network topologies, input parameters, and outputs. XMulator enhances performance accuracy by decoupling individual parts of its code, enabling accurate performance evaluation under different conditions, including the presence of faults. Its mixed-mode event processing efficiently handles both simulation events and programming language events, boosting simulation performance. The modular architecture, with its multi-layered design, ensures ease of maintenance, while extensive logging capabilities through log4net allow detailed tracing and monitoring of the simulation process.

However, the simulator's advanced features and flexible architecture can result in a steep learning curve for new users, requiring significant time and effort to master. The modular design and mixed-mode event processing, while enhancing flexibility, might introduce some performance overhead compared to specialized or optimized simulation tools. Being implemented in C#, Xmulator may not be as accessible to users familiar with other programming languages and may face limitations on platforms where C# is less commonly used. Detailed simulations and comprehensive features can demand significant computational resources, limiting large-scale or highly detailed simulations. Continuous development and maintenance are required to keep the simulator upto-date with the latest advancements in interconnection network design and simulation methodologies, which can be resource-intensive.

### **CINSim**

CINSim 48 is an advanced simulation tool designed for the detailed modeling of component-based interconnection networks. It stands out due to its ability to handle dynamic reconfiguration, allowing users to observe network behavior during changes in topology or component specifications. The simulator is capable of both steady-state and terminating simulations, which are crucial for analyzing transient behaviors in complex network systems. An additional notable feature of CINSim is its support for irregular multistage interconnection networks, enhancing its applicability beyond traditional tools that are typically limited to regular topologies. The simulator also incorporates stochastic events, facilitating more accurate and realistic performance evaluations.

The strengths of CINSim lie in its flexibility, dynamic reconfiguration, and support for both steady-state and terminating simulations. It is capable of modeling irregular multistage interconnection networks and incorporates stochastic events for more realistic performance evaluations. On the downside, CINSim have some limitations concerning the complexity associated with its extensive configurability,

potentially making it challenging for new users to navigate effectively. Furthermore, while the ability to model dynamic reconfiguration is a significant advantage, it implies increased computational demands, which could constrain performance, especially for larger network models.

The table 1 provides a detailed comparison of well-known micro-scale network simulators, highlighting their core features and outputs. This comparison includes simulators across different programming languages, years of release, and accessibility, reflecting the range of tools available for network simulation research. The table categorizes each simulator's output capabilities, such as throughput, latency, area, and power, allowing for a view of which simulators are best suited for specific evaluation needs. By consolidating these details, this comparison aids in identifying the most appropriate simulators based on project requirements and specific micro-scale network performance aspects.

# Other Simulators

There are also other notable simulators that are not widely used compared to the major simulators but offer valuable features and functionalities for specific applications. BigNetSim <sup>160</sup>, for example, is tailored for large-scale interconnection networks and utilizes optimistic parallel discrete event simulation techniques to model packet-level communication efficiently. Its high scalability and detailed network modeling make it suitable for comprehensive studies of network performance and behavior. However, BigNetSim faces challenges such as synchronization overheads during parallel execution and the potential for rollback operations that can affect performance.

NoC\_DEVS <sup>143</sup> provides a flexible and detailed component-based modeling environment based on the DEVS formalism, supporting all NoC topologies and emphasizing timing and performance metrics like delay and throughput. It offers advanced visualization capabilities and configurability, which can be beneficial for educational and detailed simulation purposes. Nonetheless, NoC\_DEVS might struggle with simulation speed for large-scale systems due to the intricate nature of DEVS modeling and could face compatibility issues when integrating with other simulation tools or models.

Other notable tools include NNSE 105 and OCIN\_TSIM 144, which offer specialized functionalities such as configurable simulation kernels and dynamic voltage and frequency scaling (DVFS), respectively. NNSE features a userfriendly GUI for easy network and traffic configuration and supports both regular and application-specific traffic patterns, although it is limited to 2D topologies and can be less effective for three-dimensional network architectures. OCIN\_TSIM emphasizes detailed power modeling and visualization capabilities but requires specific versions of libraries and software environments, which can make setup cumbersome. GPNOCSIM 107, a Java-based general-purpose NoC simulator, supports multiple topologies and provides flexible configuration options. However, its use of Java may introduce performance bottlenecks, and the uniform traffic distribution assumptions may limit its applicability for more complex traffic scenarios. Additionally, simulators like FOLCS 141 and PANE 145 provide lightweight and versatile platforms for simulating NoC architectures with

|         | _       |            |            |             |             |

|---------|---------|------------|------------|-------------|-------------|

| Tahla 1 | Foaturo | Comparison | of various | Micro-Scala | Simulators. |

|         |         |            |            |             |             |

| Name        | Year | Language     | Availability | Outputs    |          |          |       |

|-------------|------|--------------|--------------|------------|----------|----------|-------|

|             |      |              |              | Throughput | Latency  | Area     | Power |

| Supersim    | 2018 | C++          | ✓            | ✓          | <b>√</b> | Х        | Х     |

| Booksim2    | 2010 | C++          | ✓            | ✓          | <b>√</b> | Х        | Х     |

| Noxim       | 2015 | SystemC      | ✓            | ✓          | <b>√</b> | Х        | ✓     |

| Orion3      | 2015 | C and MATLAB | ✓            | Х          | Х        | <b>√</b> | ✓     |

| SunFloor-3D | 2010 | SystemC      | Х            | ✓          | <b>√</b> | Х        | ✓     |

| HNOCS       | 2012 | C++          | ✓            | ✓          | <b>√</b> | Х        | Х     |

| Nirgam      | 2007 | SystemC      | ✓            | <b>√</b>   | Х        | ✓        | Х     |

| ATLAS       | 2010 | Java         | ✓            | ✓          | <b>√</b> | Х        | Х     |

| MC-SIM      | 2008 | С            | Х            | <b>√</b>   | <b>√</b> | <b>√</b> | Х     |

| VNOC        | 2014 | C++          | ✓            | Х          | <b>√</b> | Х        | Х     |

| AcENoCs     | 2011 | HDL          | Х            | ✓          | <b>√</b> | Х        | Х     |

| DART        | 2011 | Verilog HDL  | Х            | Х          | <b>√</b> | Х        | Х     |

| NoCTweak    | 2012 | SystemC      | ✓            | ✓          | <b>√</b> | <b>√</b> | ✓     |

| DARSIM      | 2010 | C++          | Х            | ✓          | <b>√</b> | Х        | Х     |

| AdapNoC     | 2016 | Verilog HDL  | Х            | Х          | <b>√</b> | Х        | Х     |

| Garnet      | 2009 | C++          | ✓            | Х          | <b>√</b> | Х        | Х     |

| Xmulator    | 2007 | C#           | ✓            | Х          | <b>√</b> | Х        | ✓     |

| CINSim      | 2005 | C++          | X            | ✓          | <b>√</b> | X        | Х     |

a focus on FPGA implementation and asynchronous communication, respectively. FOLCS may face difficulties in accurately simulating higher-level network behaviors due to its low-level focus, and PANE may encounter issues in validating asynchronous designs against real-world performance benchmarks.

# Notable Simulators for Macro-Scale Networks

In this section, we delve into the simulators designed for larger scale and broader network environments, such as data centers, wide-area networks (WANs), and other large-scale distributed systems. These simulators provide critical insights into traffic flow management, routing efficiency, congestion control, and the scalability of network infrastructures. We will present an overview of several key macro-scale network simulators, detailing their distinctive features, strengths, and limitations. Additionally, a comparative analysis will be included to highlight the specific scenarios and conditions where each simulator excels, offering valuable guidance for researchers and engineers aiming to optimize large-scale network performance and reliability in varied contexts.

# NS-2

The Network Simulator version 2 (NS-2) was developed in 1996 as part of the VINT (Virtual Inter Network Testbed) project through a collaborative effort by the University of California at Berkeley, the University of Southern California's Information Sciences Institute, Lawrence Berkeley National Laboratory, and Xerox Palo Alto Research

Center<sup>50</sup>. NS-2 operates on event-driven principles, making it highly beneficial for researching communication networks. Leveraging OTcl for scripting flexibility and C++ for high-performance protocol implementation, NS-2 provides a robust environment with capabilities such as mobility models, energy analysis, and distinct separations between control and data planes. This combination of features has made NS-2 a widely utilized platform for evaluating network protocols and performance, benefiting from continuous improvements and adaptations over the years.

NS-2's strengths lie in its rich set of analysis tools and comprehensive network visualization capabilities, which facilitate in-depth studies and evaluations of network behaviors and performance metrics <sup>52</sup>. It supports an extensive range of protocols across all network layers, offering a vast model library that simplifies the creation of complex scenarios <sup>130</sup>. This flexibility in modeling various network environments, along with strong community support and extensive documentation, has positioned NS-2 as a cornerstone tool in network research.

However, NS-2 is not without its weaknesses. Creating simulations that strictly adhere to specific methodologies can be challenging, which may affect accuracy and reproducibility. The simulator's tracing system can be cumbersome, making debugging and analysis particularly difficult for large-scale network models. The intricate code structure further complicates this, presenting a steep barrier to new users and hindering customization efforts without a deep understanding of its architecture. Moreover, studies have highlighted issues with NS-2's TCP simulation accuracy, particularly when the first-hop link acts as a bottleneck in lower bandwidth networks like wireless and

mobile environments, potentially limiting its applicability in these scenarios.

### NS-3

Network Simulator version 3 (NS-3) is a widely used open-source network simulation tool, especially popular within the Internet of Things (IoT) domain. NS-3 is versatile, functioning both as a simulator and an emulator, allowing researchers and engineers to create operational network environments <sup>49 53 54</sup>. It supports extensive modeling capabilities for various network technologies, including TCP/IP, Wi-Fi, and wireless sensor networks, making it a powerful tool for analyzing and optimizing network performance in diverse scenarios <sup>55</sup>.

One of NS-3's key strengths is its high modularity, which facilitates easy customization and extension. This is complemented by its unique emulation mode, enabling integration with real-world network environments, which is particularly useful for testing and validation of network protocols in realistic settings. Additionally, NS-3's purely C+±based model, as opposed to NS-2's mix of object-oriented Tcl and C++, enhances performance and simplifies debugging. The provision of a Python-based scripting API further adds flexibility, allowing for easier and more diverse simulation settings.

Despite these advantages, NS-3 has some notable weaknesses. The steep learning curve associated with the programming and networking skills required for effective usage has limited its adoption in the industrial community. However, the introduction of frameworks like SIFRAN aims to mitigate this challenge by providing a no-code simulation environment for IoT networks. These frameworks enable non-programmers to leverage NS-3's capabilities through simple web interfaces, broadening its accessibility.

Moreover, the development of specialized modules, such as the Sigfox protocol simulation module, has enhanced NS-3's utility by allowing detailed modeling of energy consumption and scenario planning, critical for IoT applications. Such modules enrich NS-3's feature set, making it a more compelling choice for researchers focused on energy-efficient network design and deployment planning.

While NS-3 benefits from an active and responsive community, which is crucial for ongoing development, bug fixes, and enhancements, it does face concerns regarding reliability and limited Python scripting support. Scalability can also be an issue when simulating large networks <sup>52</sup>, which might pose challenges for extensive research projects or industrial applications.

#### ns-3 LENA

The ns-3 5G-LENA (Long-Term Evolution New Radio Access) module <sup>166</sup> is an advanced, open-source NR system-level simulator designed to facilitate research and evaluate new solutions in mobile communication networks <sup>168</sup>.. This extension of the ns-3 simulator is particularly adept at modeling the complexities of 5G networks, including features like Dual-Polarized MIMO (DP-MIMO) for enhanced data rates and realistic propagation modeling, as well as Beamforming (BF) methods using Sounding

Reference Signals (SRS) for precise channel estimation and improved network coverage in millimeter-wave and sub-6 GHz bands <sup>169</sup>. Researchers use ns-3 LENA to assess key network performance metrics such as throughput, latency, and energy efficiency across various network configurations <sup>177</sup>.

One of the module's main strengths lies in its calibration based on 3GPP specifications, ensuring that its performance aligns with industrial standards and real-world network behaviors, particularly in outdoor environments <sup>191</sup>. This alignment provides confidence in the reliability and accuracy of simulation results, bridging the gap between theoretical research and practical application. ns-3 LENA also supports a wide range of frequency bands, offering flexibility for diverse research scenarios. Additionally, it incorporates advanced protocols and mechanisms, such as mobility management and Quality of Service (QoS), allowing for comprehensive and precise simulations that reflect real-world conditions <sup>177</sup>. These capabilities enable researchers to verify and optimize network configurations effectively.

However, ns-3 5G-LENA does present certain challenges. The extensive networking and programming expertise required to use the simulator effectively can limit its adoption outside of specialized research groups. Moreover, while the integration of advanced features like DP-MIMO and BF significantly boosts its capabilities, these sophisticated models and methods demand considerable computational resources, potentially impacting the scalability of simulations for very large networks.

#### COOJA

The COOJA simulator <sup>193</sup>, closely integrated with the Contiki OS, is a prominent tool for simulating sensor networks, particularly focusing on resource-constrained devices. With its event-driven approach, COOJA facilitates efficient execution and detailed system behavior tracking. It supports pre-emptive multithreading on a per-process basis, allowing for the simulation of concurrent processes within each sensor node. This makes it particularly effective for studying complex, concurrent operations in sensor networks. Additionally, it features a comprehensive implementation of the TCP/IP protocol stack, which can be extended using custom interfaces to represent various sensor node properties, such as location, user interactions, and radio transceivers, thus offering a high degree of modularity for researchers <sup>177</sup>.