# OSM: Off-Chip Shared Memory for GPUs

Sina Darabi, Ehsan Yousefzadeh-Asl-Miandoab<sup>®</sup>, Negar Akbarzadeh, Hajar Falahati<sup>®</sup>, Pejman Lotfi-Kamran<sup>®</sup>, Mohammad Sadrosadati<sup>®</sup>, and Hamid Sarbazi-Azad<sup>®</sup>

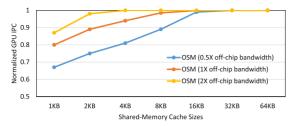

Abstract—Graphics Processing Units (GPUs) employ a shared memory, a software-managed cache for programmers, in each streaming multiprocessor to accelerate data sharing among the threads in a thread block. Although 60% of the shared memory space is underutilized, on average, there are some workloads that demand higher shared memory capacities. Therefore, improving shared memory utilization while satisfying the needs of shared memory intensive workloads is challenging. We make a key observation that the lifetime of each shared memory address is significantly shorter than the execution time of a thread block. In this paper, we first propose Off-Chip Shared Memory (OSM) that allocates shared memory space in the off-chip memory, and accelerates accesses to it via a small on-chip cache. Using an 8 KB cache for shared memory addresses, OSM provides almost the same performance as the baseline GPU that uses 96 KB on-chip shared memory. OSM improves GPU performance in two ways. First, it allocates higher shared memory capacities in the off-chip memory, and improves thread-level parallelism (TLP). Second, it designs a unified cache for shared memory and global address spaces, providing more caching space for global memory address space even for the workloads with high shared memory utilization. Our experimental results show an average 21% and 18% IPC improvement compared to the baseline and the state-of-the-art architectures.

Index Terms—Cache memory, GPUs, lifetime, off-chip memory, shared memory

#### 1 Introduction

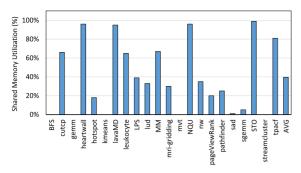

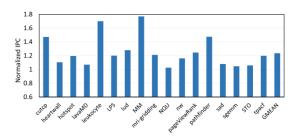

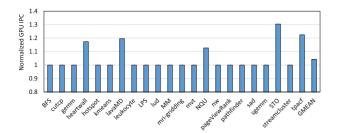

¬PUs employ a shared memory in each streaming multi-Jprocessor (SM). Shared memory is a software-managed cache (a.k.a. scratch-pad memory) that programmers usually use to accelerate data sharing across threads of a thread block. In addition, using the shared memory rather than the main memory helps to save significant amount of GPU power. It is due to the fact that every access to the main DRAM memory consumes considerable amount energy [11], [12], [31], [52]. On the contrary, shared memory exacerbates the under-utilization of GPU resources due to two main reasons [1], [10], [20], [37], [59], [61]. First, there are many GPU workloads, e.g. graph applications [70], that under-utilize the shared memory. Our experiments across five benchmark suites indicate that most of the workloads do not fully utilize the allocated shared memory space. According to the Fig. 1, on average only 39.5% of the shared memory space is utilized across 22 workloads. Second,

Sina Darabi, Ehsan Yousefzadeh-Asl-Miandoab, and Negar Akbarzadeh are with the Department of Computer Engineering, Sharif University of Technology, Tehran 11155-9517, Iran. E-mail: {sinad1367, ehsanyusefzadehasl, n.akbarzadeh93}@gmail.com.

Manuscript received 13 Jan. 2021; revised 8 Jan. 2022; accepted 7 Feb. 2022. Date of publication 24 Feb. 2022; date of current version 15 June 2022.

The work of Pejman Lotfi-Kamran was supported by a Grant from Iran National Science Foundation (INSF).

(Corresponding author: Mohammad Sadrosadati.) Recommended for acceptance by M. Becchi.

Digital Object Identifier no. 10.1109/TPDS.2022.3154315

insufficient shared memory capacity can limit the number of allocated thread blocks in each SM, and potentially TLP [44]. This results in under-utilization of different GPU resources, e.g. execution units, register file, and memory bandwidth. Although enlarging shared memory capacity can help to improve TLP, it degrades resource-utilization of workloads that do not take advantage of a larger shared memory.

Several attempts have been accomplished by both industry and academic researches to address the aforementioned issues [10], [20], [37], [59], [61]. NVIDIA Kepler [3] architecture unifies shared memory and L1 data cache memory in each SM. This unified memory has 64 KB capacity, and programmers can select one of the 3 possible shared memory/ L1 cache configurations: 16 KB/48 KB, 32 KB/32 KB, and 48 KB/16 KB. This solution is not optimal for the cases in which programmers do not utilize the minimum 16 KB portion of the shared memory. Some of the prior works use virtualization, such as [59], [61], while some others, such as [20], [37], propose new structures, and others exploit time-multiplexing approaches [71]. Shoushtari et al. [59] propose a virtualization framework which relocates the shared memory to off-chip memory, and hence, provides an unlimited resource illusion to all threads. Vijaykumar et al. [61] propose a virtualization framework that provides unlimited resource (e.g. shared memory, register, and threads) illusion. These works can improve TLP for shared memory intensive applications; however, a significant amount of large on-chip storage space is still wasted for the workloads that under-utilize the shared memory. Gebhart et al. [20] unify L1 data cache, shared memory, and register file. This work can increase shared memory capacity and utilization rate at the same time. NVIDIA Volta architecture [1] also provides 128 KB on-chip storage per SM unified across shared memory, L1 data cache, and texture cache,

Hajar Falahati, Pejman Lotfi-Kamran, and Mohammad Sadrosadati are with the School of Computer Science, Institute for Researches in Fundamental Sciences (IPM), Tehran 19538-33511, Iran. E-mail: {hajar.falahati, m.sadr89}@gmail.com, plotfi@ipm.ir.

<sup>•</sup> Hamid Sarbazi-Azad is with the Department of Computer Engineering, Sharif University of Technology, Tehran 11155-9517, Iran, and also with the School of Computer Science, Institute for Researches in Fundamental Sciences (IPM), Tehran 19538-33511, Iran. E-mail: azad@ipm.ir.

Fig. 1. Shared memory utilization across 22 workloads; 5 workloads out of 22 do not utilize shared memory at all.

that can support several shared memory/L1 cache/texture cache configurations. The allocatable space for shared memory per SM can be in the range of 0 KB to 96 KB. As a result, the whole 128 KB on-chip memory space can be used for L1 data and texture caches in applications that do not employ shared memory.

The main bottleneck of both works reported in [20] and [1] is that the shared memory space is allocated statically for each thread block, and thus, it will not be freed till the end of the thread block execution. This shortcoming can greatly reduce the effectiveness of these solutions if shared memory addresses experience a short lifetime range. Komuravelli et al. [37] propose a new on-chip memory structure, stash, to address visibility through specialized memory spaces in heterogeneous systems. Stash unifies the specialized memory components (data cache and shared memory) in a coherent address space. The unified structure needs both hardware and software supports and treats all memory accesses, either data cache or shared memory, likely. Our evaluation results show that these memory accesses have various lifetime ranges and we need to modify the cache management. However, none of the abovementioned works have a solution to deal with various lifetime ranges in shared memory accesses.

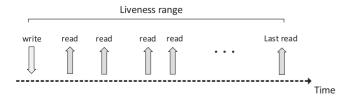

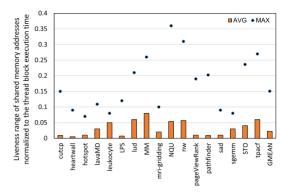

The lifetime range of a location is the time duration between its first write and last read, as shown in Fig. 2. To compare the lifetime range of shared memory addresses with the execution time of a thread block, we measure lifetime range of shared memory addresses for each workload and normalize it to its average thread block execution time. We use Accel-Sim [34] for this experiment. Fig. 3 reports the average results for 14 workloads. Note that only the workloads that use shared memory during their execution, are evaluated. We make an observation that, on average, the lifetime range of shared memory addresses is about 50× shorter than the thread block execution time, underscoring the fact that we do not need to keep these addresses for the entire execution time of a thread block.

Fig. 2. lifetime range of a shared memory address.

Fig. 3. Average and maximum lifetime range of shared memory addresses for the workloads that utilize shared memory.

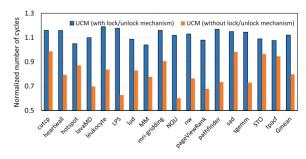

Based on our key observation we propose Off-Chip Shared Memory (OSM) that improves capacity and utilization of shared memory at the same time. OSM allocates shared memory address space to off-chip memory and accelerates shared memory accesses using a small on-chip cache. Note that we do not need a dead shared memory address for the rest of the execution. However, since we cannot be 100% sure that a shared memory address is dead, we propose to keep shared memory addresses in the off-chip memory to be able to service any unpredictable future accesses. The key challenge is that the mechanism can increase bandwidth usage due to frequent evictions and insertions of data items in shared memory cache. Note that the first insertion has no overhead compared to the baseline GPU architecture, as the baseline also consumes memory bandwidth to move data from the global memory to the shared memory. To lessen this overhead, OSM attempts to keep addresses in the shared memory cache for their entire lifetime range, and prevent re-inserting them. Studying access patterns of shared memory addresses reveal that some addresses are accessed only a few number of times during their lifetime range. As a result, such addresses can quickly become the head of the least recently used (LRU) queue, and are evicted before elapsing their lifetime range. To deal with this issue, we devise a lock/unlock mechanism on top of LRU replacement policy. In this approach, only unlocked addresses at the head of LRU queue can be evicted. In the next step, we propose a unified on-chip memory for handling shared and global accesses; this unified on-chip memory provides a larger level-1 cache with higher bandwidth resulting in better performance.

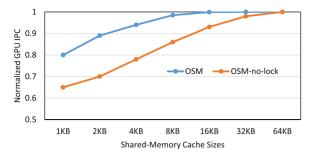

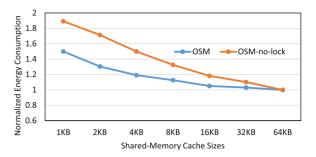

Our experimental results show that with an 8 KB shared memory cache per SM, we can achieve almost the same performance as the baseline NVIDIA Volta GPU that can employ up to 96KB [1] on-chip shared memory per SM. We use OSM to (1) allocate larger shared memory space in the off-chip memory which allows scheduling more thread blocks for shared memory intensive workloads, and (2) design a unified cache memory for both shared memory and global memory address spaces, improving caching space and better utilization for the workloads with low shared memory utilization. Our experimental results show that our proposal improves GPU performance by 21% and 18%, on average, compared to the baseline GPU and the state-of-the-art proposal, respectively.

It should be noted that Our proposal is agnostic to NUMA in multi-chip-module GPUs. Since in such

Fig. 4. GPU architecture.

architectures, each GPU has its own device memory, and we make sure to allocate shared memory addresses of each GPU to its memory. As a result, our proposal does not generate remote traffic for reading shared memory addresses.

We make the following contributions:

- We thoroughly study shared memory and the lifetime of its addresses across several workloads. We observe that the lifetime range of shared memory addresses is significantly shorter than thread block execution time.

- We propose OSM that allocates shared memory space in the off-chip memory, and accelerates its accesses using a small on-chip cache. We devise a lock/unlock mechanism on top of LRU replacement policy to prevent addresses from being evicted before their lifetime is elapsed.

- We use OSM to improve GPU's TLP and allocate more caching space

to global memory address space.

Our proposal improves GPU performance by 21% and 18%, on average, compared to the baseline GPU and the state-of-the-art proposal, respectively.

#### 2 BACKGROUND

In this section, we present the needed background on the GPU architecture and shared memory.

#### 2.1 GPU Architecture

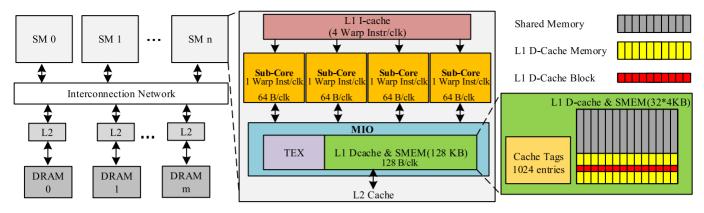

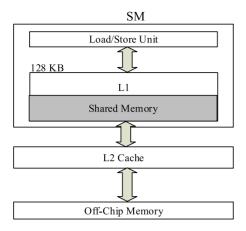

GPU kernels are composed of many Single-Program Multiple-Data (SPMD) threads grouped by the programmer into several Thread Blocks or Cooperative Thread Arrays (CTAs). Each CTA is assigned to a Streaming Multiprocessor (SM) upon thread launch. SMs are SIMD processing units with dedicated fast memory units. During execution, threads assigned to each SM are divided into multiple fixed length (e.g., 32) groups. Each group of threads is called a warp (NVIDIA terminology) or wavefront (AMD terminology). Threads inside a warp are executed in parallel lockstep manner, where each thread executes the same instruction. SIMD units are time-multiplexed between different warps. In each cycle, the GPU selects one warp to be executed based on the GPU's warp scheduling policy following the SIMT model. In the SIMT model, all threads of a warp execute the same instruction on different data, but threads of a warp may take different control flow paths, leading to idle SIMD lanes (called branch divergence). SMs are responsible for the execution of warps. Each SM is composed of several components, including SIMD integer/floating-point units, load/store units, special function units, L1 data and instruction caches, local shared memory, and a register file that is responsible for maintaining the context of all threads inside the SM. Fig. 4 shows the GPU architecture evaluated in our study, modeled after the NVIDIA Volta GPU architecture. SMs are connected to L2 banks with an on-chip interconnection network.

## 2.2 GPU Memory System

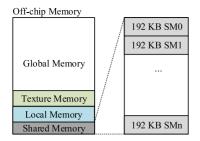

A thread commonly accesses local, shared, and global data through a rich memory hierarchy shown in Fig. 4. The GPU architecture depicted in Fig. 4 is adapted from NVIDIA Volta architecture [1]. The local data is usually placed in a dense register file for fast context switching. An SM (streaming multiprocessor) is also associated with a software-managed local memory called Shared Memory for shared data accesses by the threads within a block. The shared memory/L1 is composed of 32 four-byte-width blocks. Each block contains 4 KB of data. Since a unified on-chip memory space is used for shared memory and L1-D cache, and programmer specifies the shared memory capacity, the rest of the unified on-chip memory space is dedicated to L1 cache, automatically. The gray and yellow parts of the unified onchip memory space shown in Fig. 4 is dedicated to shared memory and L1-D cache, respectively. Since the minimum acceptable L1 cache size is 32 KB in Volta architecture, the shared memory capacity can be in the range of 0-96 KB. Therefore, in some cases that we do not need shred memory at all, we can assign the whole 128 KB on-chip cache space to the L1 cache. Since the capacity of an L1 cache block (depicted by red in Fig. 4) is 128B, assuming that the whole 128 KB on-chip cache space is dedicated to L1, we need 1024 entries for the tags. Global data refers to the data shared among all threads within a grid. When a thread requests data from off-chip main memory, the accesses pass through a two-level cache hierarchy. The L1 caches are private to SMs with no coherency among them. The L2 cache is a banked cache array that is shared by all SMs and uses write-back policy with respect to main memory. Each L2 bank communicates with L1 cache of each core through an interconnection network. Knowing the fact that each SM

(a) Volta GPU Memory System

Fig. 5. Baseline GPU memory system vs. OSM memory system.

consists of 4 sub-cores, the memory input/output unit (MIO) serves, at maximum, 64B requests from each sub-core per clock. If the requests are distributed evenly among the 32 blocks of L1-D cache/shared memory, the maximum bandwidth (128B/clock) can be achieved. Note that due to the 128B/clock bandwidth limit, the four sub-cores cannot serve 64B requests, simultaneously. L1-D cache and shared memory use the same 32-bank memory structure (4 KB capacity per bank) as shown in Fig. 4; however, they have some differences. We can access 32-bit shared memory arrays via a thread-index directly, while for accessing L1-D cache, we should read 128B (four 32B sectors) of the cache block. In addition, L1 cache requires an extra hardware for managing tags and implementing LRU replacement policy.

## 2.3 Shared Memory

GPU programmers use shared memory to accelerate data sharing and synchronization across threads in a thread block. Shared memory capacity is one of the main TLP limitation factors as it can limit the number of thread blocks allocated to each SM. Shared memory is a multi-banked memory that can serve multiple conflict-free requests in parallel. Thread-index of a thread inside a thread block is used to access its corresponding shared data arrays. However, different thread blocks cannot share their data using the shared memory. In fact, if data locality exists across thread blocks rather than inside a thread block, it is not efficient to store the data in the shared memory. To move a variable from global memory to the shared memory, GPU needs to load it to a register and then store the register value in the shared memory. Therefore, due to the high cost of moving data from global memory to the shared memory, storing data with low reusability in the shared memory would result in performance overhead instead.

Despite all the performance benefits that shared memory provides, it has some programming burden; first, programmers should handle the shared memory accesses with no bank conflicts. Second, programmers should not overestimate the shared memory capacity per thread block to provide enough TLP for the performance. The number of thread blocks that can be assigned to an SM is determined

(b) OSM Memory System

by the number of factors including available register per thread, maximum number of supportable threads, maximum number of supportable CTAs and shared memory capacity. In fact, due to the limited capacity of on-chip shared memory, over-allocating shared memory for thread blocks can limit the total number of thread blocks and accordingly sacrifice the TLP.

# 3 OFF-CHIP SHARED MEMORY (OSM)

Fig. 3 shows that the lifetime range of shared memory addresses are too short to keep them on-chip throughout the execution time of a thread block. We propose OSM that allocates shared memory address space in the off-chip memory and accelerates its accesses using an on-chip shared memory cache. Only threads inside one thread block can access the off-chip shared memory space.

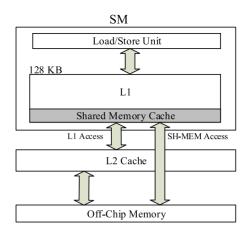

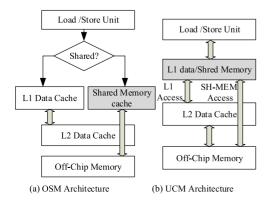

Fig. 5 indicates the difference between the baseline GPU and the proposed OSM architecture. In the baseline Volta architecture [1], we need to specify the L1 cache and shared memory space statically before running the program. However, in the proposed architecture, we can dynamically assign the available space to L1 cache or shared memory according to the requirements of the running application. For simplicity, we employ the same configuration as the L1-D cache for implementing our shared memory cache in each SM. Therefore, our shared memory cache has 64 ways. It should be noted that the accesses to the shared memory and L1 cache are still similar to the baseline architecture. The only difference is the metadata required for implementing OSM. In fact, for lock/unlock mechanism, we need to add one bit to each cache block tag.

Since shared memory addresses are shared only across threads in a thread block of an SM, we utilize a write-back policy for the added shared memory cache. Therefore, we only write data in the shared memory cache at the request time. Data will be written back to the shared memory space of off-chip memory on its eviction at some later time. If a request misses in the shared memory cache, we need to access the off-chip DRAM to service it. Note that in OSM, we need to write each *dirty* evicted shared memory address into the off-chip memory as we cannot guarantee that the

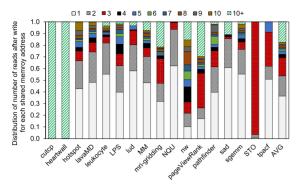

Fig. 6. Distribution of read accesses during their lifetime range for the workloads that utilize the shared memory during the execution.

address will not be accessed in the future. The shared memory accesses which are evicted or missed in the on-chip shared memory, simply bypass the L2 cache and directly go to the off-chip shared memory.

To reduce the overhead of evictions and re-insertions, OSM needs to keep each shared memory address in the cache during its lifetime range. Evicting a shared memory address before end of its lifetime period, or keeping it more than its lifetime period can potentially impose performance and energy overheads. This is due to the 2 main reasons. First, the former can potentially cause misses in the shared memory cache. This can increase the bandwidth usage and the average shared memory access latency, which indeed, imposes performance and energy overheads. Second, the latter also reduces the effectiveness of our technique and induces the need for larger shared memory caches. As a result, it is necessary to track the lifetime range of each address and consider it in the cache replacement policy.

Unfortunately, run-time measurement of lifetime ranges is impractical due to the 2 main reasons. First, we do not exactly know which shared memory read access is the last read request. Second, keeping a counter per shared memory cache block imposes a significant overhead. Therefore, we devise to predict the lifetime ranges through studying the write/read pattern of shared memory addresses. We count the number of read accesses for each shared memory address before its lifetime is elapsed for each workload. Fig. 6 shows the distribution of read accesses during their lifetime ranges for each workload. We observe that for some workloads, such as LPS, NQU, and sad, more than 60% of shared memory addresses have up to two reads during their lifetime range. This low number of accesses can cause quick eviction of a shared memory address, based on the baseline replacement policy (LRU). We propose to lock a shared memory address in the cache when it is written, in order not to be selected for eviction, and unlock it after a certain number of reads. We use a threshold, called #readsto-unlock, to decide after how many reads a shared memory address can be unlocked. We statically set this threshold to one. We analyze the sensitivity of our proposal to this threshold value in Section 6.4. Those shared memory addresses that have frequent reads during their lifetime range, say more than 10 accesses, are likely kept in the cache based on the LRU replacement policy. As a corner case, it is probable that all cache blocks in a cache set are locked, and hence, there is no room for new insertion. In this case, OSM

TABLE 1 Memory Latency

| Cache Type             | Miss penalty<br>(L2 hit) | Miss penalty (main memory hit) | Hit<br>latency |

|------------------------|--------------------------|--------------------------------|----------------|

| Shared Memory<br>Cache | _                        | 310 cycle                      | 28 cycle       |

| L1 Data Cache          | 193 cycle                | 470 cycle                      | 28 cycle       |

evicts one of these locked cache blocks based on the LRU replacement policy. It should be noted that we do not observe such a case in the tested workloads. We just consider it as a probable case that might happen in other applications.

## 4 OSM USECASES

In this section, we study how OSM can be employed to improve GPU performance. OSM has two main advantages. First, since OSM moves the shared memory address space to off-chip memory, we would have an extremely larger space in the off-chip memory for shared memory addresses than the limited on-chip SRAM space. This can potentially improve the thread-level parallelism (TLP), and accordingly the performance of the workloads whose number of thread blocks is limited by the insufficient on-chip shared memory space. We analyze the effect of this advantage on the GPU performance in Section 6.1. Moreover, we analyze the access latency of the L1-D cache and shared memory cache. Table 1 reports the access latency of the L1-D cache and shared memory cache when hit/miss happens. As Volta supports GPU memory over-subscription, we need a TLB for the cases where the unified memory feature is enabled. This leads to the worst access latency of the GPU memory hierarchy since it is needed to access the TLB to find the location of the requested address. Therefore, we measure the latency of L1 cache in the worst-case scenario. Since both the L1 cache and shared memory use the same memory structure, they have the same hit latency (28 cycles). But different scenarios happen in the case of miss. For L1-D cache miss, if the data hits in L2, the miss penalty would be about 193 cycles. Otherwise, we should get the data from the main memory after 470 cycles. Fortunately, on a shared memory cache miss, the access will be sent directly to the main memory as we bypass L2. The miss penalty, in this case, would be about 310 cycles. According to the obtained results, we can conclude that the miss penalty of the shared memory cache in OSM is less than the miss penalty of the L1 cache when data also misses in L2.

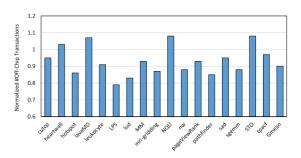

Second, since we are using a cache memory for shared memory addresses, we can combine the L1 data cache and shared memory, and manage global/local memory and shared memory addresses in different spaces of off-chip memory, as shown in Fig. 7. Note that we do not allocate shared memory space inside the global memory space, rather we allocate shared memory space inside the off-chip memory (a.k.a., device memory). The off-chip memory is used for keeping different memory address spaces, such as global, local, texture, etc. In OSM, we propose to keep shared memory space in the off-chip memory as well. So,

Fig. 7. Unified addressing map to off-chip memory (a.k.a., device memory).

this does not need significant changes in the hardware and the address mapping. Distinguishing across these address spaces is performed based on each address range. We move forward and improve our design by unifying the shared memory cache and L1-D cache (called UCM, or unified cache memory). Despite OSM that only provides 8 KB 1-set on-chip shared memory caching space, with UCM we can have 128 KB 16-set unified on-chip shared memory/L1 cache space. UCM outperforms OSM in case of performance since it satisfies shared memory accesses dynamically using a much smaller on-chip space, while it also provides larger caching space for the global memory address space. Fig. 8 indicates the block diagram of memory access hierarchy in OSM and UCM. Since there is a limited L2 cache space, we bypass the L2 cache for accesses to the off-chip shared memory. Bypassing the L2 cache is already implemented in current GPU architectures and there is no need to any additional hardware changes. It should be noted that the depicted lines between the blocks of the figure are just showing the logical connection of the blocks.

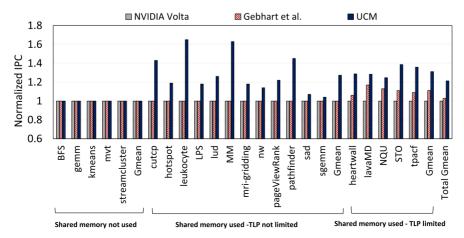

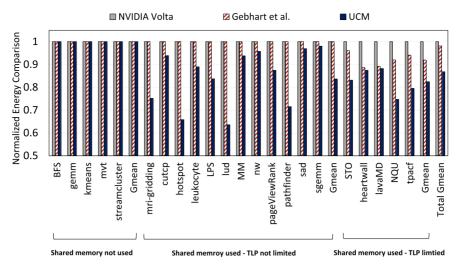

To show the maximum achievable performance improvement for workloads that both utilize shared memory and L1 cache simultaneously, we suppose 96 KB of shared memory (like the case of baseline Volta architecture [1]) and on the other hand, increase the L1 cache capacity from 32 KB to 128 KB. Fig. 9 indicates the performance results of this ideal case. It can be seen that performance improves up to 77% (23.5%, on average) to which we should try to approach utilizing UCM architecture.

#### 5 METHODOLOGY

**Simulation.** We evaluate OSM and UCM using Accel-Sim [34] modeling an NVIDIA Volta-like configuration [2],

Fig. 8. Unified L1 data cache and shared memory cache.

Fig. 9. Performance improvement of an idealized GPU with 96 KB shared memory and 128 KB L1 data cache compared to the baseline Volta architecture for the workloads that utilize the shared memory.

[25]. Table 2 reports the main simulation parameters. NVI-DIA Volta V100 GPU comes with two configurations: 16 GB and 32 GB HBM memory [2]. However, we choose 32 GB for our experiments, so that all evaluated datasets can fit into the HBM memory. Moreover, according to the cache configurations provided in Table 2, GPU caches have relatively large associativity. This is due to the fact that (1) GPUs can tolerate higher memory access latencies and are less latency-sensitive [33], [42]. (2) GPU caches normally suffer from thrashing that can be alleviated by utilizing large associativity degrees [76]. (3) Inter-thread locality can be captured via large associativity degrees [38], [76].We modified Accel-Sim to support the proposed design. We suppose the access latency of the shared memory cache is the same as other on-chip caches in GPU. We treat off-chip shared memory accesses exactly like the off-chip memory accesses in GPUs. We calculate GPU energy consumption by multiplying the execution time extracted from Accel-Sim to GPU power consumption extracted from GPU-Wattch [29]. GPUWattch [29] reports the consumed power for all GPU components (i.e., different storage spaces, processing units, memory controllers, and network-on-chip). Compared to the baseline GPU, the proposed idea affects the power consumption of the components in the memory system and the execution units. The power consumption of the memory system is affected based on two main reasons. First, UCM adds some power consumption due to multiple insertions and evictions of shared memory addresses in the cache. Second, UCM can reduce the power consumption of the memory system due to improving the hit rate of the L1 data cache. Regarding the execution units, UCM usually

TABLE 2 Configuration Parameters of Baseline Architecture

| Parameter                   | Value                                      |  |

|-----------------------------|--------------------------------------------|--|

| Number of SM                | 80                                         |  |

| Core clock                  | 1132 MHz                                   |  |

| Scheduler                   | GTO                                        |  |

| Number of schedulers per SM | 4                                          |  |

| Number of warps per \$M     | 64                                         |  |

| Register file size          | 256 KB per SM                              |  |

| Shared memory size          | up to 96 KB per SM                         |  |

| L1 data cache               | 64-way, up to 128 KB, 128B line            |  |

| L1 instruction cache        | 16-way, 128 KB, 128B line                  |  |

| LLC                         | 24-way, 6 MB, 128B line                    |  |

| Memory model                | 32 GB HBM2.0,                              |  |

| · ·                         | FR-FCFS, 850 MHZ                           |  |

| HBM timing                  | $t_{CL}$ =12, $t_{RP}$ =12, $t_{RC}$ =40,  |  |

| _                           | $t_{RAS}$ =28, $t_{RCD}$ =12, $t_{RRD}$ =3 |  |

TABLE 3 Workloads

| Workload           | Foot print (per SM) | Category (shared memory used)                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|---------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BFS [9]            | 433 KB              | Shared memory is not used (0)                    | This workload performs breadth-first search on a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| [21]               | 2145 I/D            | Chanad manageria natural (0)                     | graph  Matrix multiply Coalpha A Bubata C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| gemm [21]          | 3145 KB<br>6579 KB  | Shared memory is not used (0)                    | Matrix-multiply C=alpha.A.B+beta.C<br>A clustering algorithm used extensively in data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| kmeans [13]        | 03/9 KD             | Shared memory is not used (0)                    | mining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| mvt [21]           | 2164 KB             | Shared memory is not used (0)                    | Matrix Vector Product and Transpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| streamCluster [13] | 236 KB              | Shared memory is not used (0)                    | A solver ro the online clustering problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| cutcp [60]         | 193 KB              | Shared memory is used TLP is                     | Computes the short-range component of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| careh [00]         | 1,0112              | not limited (32 KB)                              | Coulombicpotential at each grid point over a 3D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    |                     | , ,                                              | gridcontaining point charges representing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |                     |                                                  | anexplicit-water biomolecular model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| hotspot [13]       | 349 KB              | A Shared memory is used TLP is                   | A thermal simulation tool for estimating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| •                  |                     | not limited (32 KB)                              | processor temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| leukocyte [13]     | 184 KB              | Shared memory is used TLP is                     | Medical Imaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    |                     | not limited (32 KB)                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LPS [9]            | 1137 KB             | Shared memory is used TLP is                     | 3D Laplace Solver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1 1[10]            | 0/1 I/D             | not limited (64 KB)                              | TIT I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| lud [13]           | 261 KB              | Shared memory is used TLP is                     | LU decomposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MM [22]            | 274 KB              | not limited (96 KB)                              | A dance matrix multiplication using the standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MM [23]            | 2/4 ND              | Shared memory is used TLP is not limited (64 KB) | A dense matrix multiplication using the standard BLAS format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| mri-gridding [60]  | 1088 KB             | Shared memory is used TLP is                     | Computes a regular grid of data representing an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |